коэффициент многопроцессорного потока какой должен быть

О потоках в процессоре

Добрый день. Сегодня хотелось бы разобрать, что такое потоки в процессоре. Те самые, о функциях и возможностях которых большинство и не догадывается, однако любят хвастаться остальным.

Если провести сравнение процессоров разных поколений, то можно заметить одну интересную тенденцию: многопоточность – штука полезная и здорово повышает суммарную производительность системы.

Начнем с того, что каждый современный процессор построен на физических ядрах с определенной частотой. Допустим, 1 ядро имеет тактовую частоту в 3 ГГц, т.е. может выполнить 3 млрд вычислительных операций за секунду (такт). Но современные ОС (Windows, Linux, MacOS) запускают более 3 млрд процессов, т.е. пользователь начинает сталкиваться с таким понятием как прерывание: ЦП физически не успевает обрабатывать все сразу и начинает переключаться на самые приоритетные задачи.

Логика здесь элементарная: присмотреться к многоядерным и многопоточным решениям. Разгон не дает линейного прироста в производительности, иначе такие гиганты как Intel и AMD выпускали бы процессоры на 5-6 и более ГГц.

Польза от повышения частоты есть, но она нивелируется увеличенным энергопотреблением и сокращением срока службы ЦП.

Многопоточность и все о ней

Многие наверняка слышали выражения из серии «2 потока», «4 потока», «8 потоков» и т.д. При этом физических ядер зачастую было в 2 раза меньше.

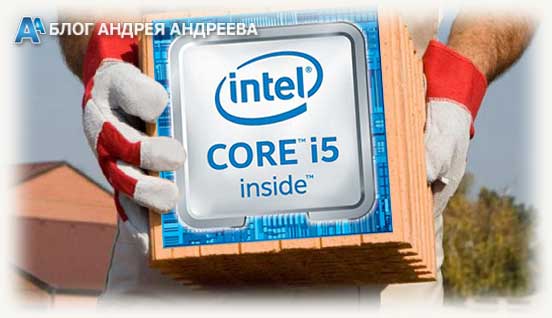

Эта технология имеет название HyperThreading (Intel) или SMT (AMD).

Многопоточность у красных появилась совсем недавно, с выходом чипов Ryzen на совершенно новом техпроцессе. Что это такое – тема отдельной статьи.

Цель функции заключается в том, что на 1 ядро может одновременно обрабатывать несколько потоков данных. Пока первый поток простаивает, а второй занимается вычислением, запущенное приложение может воспользоваться вакантной логической мощью для своих целей. В результате, прерывания случаются гораздо реже, а вы не ощущаете тормозов и прочих неудобств при работе.

Недостаток технологии заключается в следующем:

Знакомы с понятием Turbo Boost? Процесс кратковременно повышает частоту процессора на несколько сотен мегагерц в особо сложных сценариях, чтобы вы не испытывали проблем при обработке сложных данных.

Сколько нужно ядер и потоков современному обывателю?

Как я уже сказал выше, современные ОС падки на ресурсы процессора, поскольку отнимают часть мощностей на собственные службы, интерфейс, красивости и функции защиты в реальном времени. Но при этом пользователь хочет еще и работать с комфортом.

Вместо итогов

Практика показывает, что современный универсальный ПК должен иметь в своем распоряжении как минимум 4 ядра/8 потоков, чего будет достаточно для большинства задач, связанных с обработкой данных. Хотя варианты из серии 6/12 выглядят более обещающими по той причине, что стоят они не намного дороже, а пользы от них больше.

В качестве «золотой» середины можем предложить свежий вариант модели, построенный на обновленной архитектуре Zen2. Он отлично справляется с играми, программами, распараллеливанием и обработкой данных, при этом отлично гонится(одним словом — стал популярным (появился в июле 2019)).

Надеемся, что вы почерпнули для себя полезную информацию, которая пригодится при подборе процессора для будущей системы. Следите за дальнейшими обновлениями, чтобы не пропустить новые статьи об анатомии ЦП.

Высокопроизводительные вычисления: проблемы и решения

Компьютеры, даже персональные, становятся все сложнее. Не так уж давно в гудящем на столе ящике все было просто — чем больше частота, тем больше производительность. Теперь же системы стали многоядерными, многопроцессорными, в них появились специализированные ускорители, компьютеры все чаще объединяются в кластеры.

Зачем? Как во всем этом многообразии разобраться?

Что значит SIMD, SMP, GPGPU и другие страшные слова, которые встречаются все чаще?

Каковы границы применимости существующих технологий повышения производительности?

Введение

Откуда такие сложности?

Формула производительности

Возьмем самую общую формулу производительности:

Видим, что производительность можно измерять в количестве выполняемых инструкций за секунду.

Распишем процесс поподробнее, введем туда тактовую частоту:

Первая часть полученного произведения — количество инструкций, выполняемых за один такт (IPC, Instruction Per Clock), вторая — количество тактов процессора в единицу времени, тактовая частота.

Таким образом, для увеличения производительности нужно или поднимать тактовую частоту или увеличивать количество инструкций, выполняемых за один такт.

Т.к. рост частоты остановился, придется увеличивать количество исполняемых «за раз» инструкций.

Включаем параллельность

Как же увеличить количество инструкций, исполняемых за один такт?

Очевидно, выполняя несколько инструкций за один раз, параллельно. Но как это сделать?

Все сильно зависит от выполняемой программы.

Если программа написана программистом как однопоточная, где все инструкции выполняются последовательно, друг за другом, то процессору (или компилятору) придется «думать за человека» и искать части программы, которые можно выполнить одновременно, распараллелить.

Параллелизм на уровне инструкций

Возьмем простенькую программу:

a = 1

b = 2

c = a + b

Первые две инструкции вполне можно выполнять параллельно, только третья от них зависит. А значит — всю программу можно выполнить за два шага, а не за три.

Процессор, который умеет сам определять независимые и непротиворечащие друг другу инструкции и параллельно их выполнять, называется суперскалярным.

Очень многие современные процессоры, включая и последние x86 — суперскалярные процессоры, но есть и другой путь: упростить процессор и возложить поиск параллельности на компилятор. Процессор при этом выполняет команды «пачками», которые заготовил для него компилятор программы, в каждой такой «пачке» — набор инструкций, которые не зависят друг от друга и могут исполняться параллельно. Такая архитектура называется VLIW (very long instruction word — «очень длинная машинная команда»), её дальнейшее развитие получило имя EPIC (explicitly parallel instruction computing) — микропроцессорная архитектура с явным параллелизмом команд)

Самые известные процессоры с такой архитектурой — Intel Itanium.

Есть и третий вариант увеличения количества инструкций, выполняемых за один такт, это технология Hyper Threading В этой технологии суперскалярный процессор самостоятельно распараллеливает не команды одного потока, а команды нескольких (в современных процессорах — двух) параллельно запущенных потоков.

Т.е. физически процессорное ядро одно, но простаивающие при выполнении одной задачи мощности процессора могут быть использованы для выполнения другой. Операционная система видит один процессор (или одно ядро процессора) с технологией Hyper Threading как два независимых процессора. Но на самом деле, конечно, Hyper Threading работает хуже, чем реальные два независимых процессора т.к. задачи на нем будут конкурировать за вычислительные мощности между собой.

Технологии параллелизма на уровне инструкций активно развивались в 90е и первую половину 2000х годов, но в настоящее время их потенциал практически исчерпан. Можно переставлять местами команды, переименовывать регистры и использовать другие оптимизации, выделяя из последовательного кода параллельно исполняющиеся участки, но все равно зависимости и ветвления не дадут полностью автоматически распараллелить код. Параллелизм на уровне инструкций хорош тем, что не требует вмешательства человека — но этим он и плох: пока человек умнее микропроцессора, писать по-настоящему параллельный код придется ему.

Параллелизм на уровне данных

Векторные процессоры

Мы уже упоминали скалярность, но кроме скаляра есть и вектор, и кроме суперскалярных процессоров есть векторные.

Векторные процессоры выполняют какую-то операцию над целыми массивами данных, векторами. В «чистом» виде векторные процессоры применялись в суперкомьютерах для научных вычислений в 80-е годы.

По классификации Флинна, векторные процессоры относятся к SIMD — (single instruction, multiple data — одиночный поток команд, множественный поток данных).

В настоящее время в процессорах x86 реализовано множество векторных расширений — это MMX, 3DNow!, SSE, SSE2 и др.

Вот как, например, выглядит умножение четырех пар чисел одной командой с применением SSE:

float a[4] = < 300.0, 4.0, 4.0, 12.0 >;

float b[4] = < 1.5, 2.5, 3.5, 4.5 >;

__asm <

movups xmm0, a ; // поместить 4 переменные с плавающей точкой из a в регистр xmm0

movups xmm1, b ; // поместить 4 переменные с плавающей точкой из b в регистр xmm1

mulps xmm1, xmm0 ; // перемножить пакеты плавающих точек: xmm1=xmm1*xmm0

movups a, xmm1 ; // выгрузить результаты из регистра xmm1 по адресам a

>;

Таким образом, вместо четырех последовательных скалярных умножений мы сделали только одно — векторное.

Векторные процессоры могут значительно ускорить вычисления над большими объемами данных, но сфера их применимости ограничена, далеко не везде применимы типовые операции над фиксированными массивами.

Впрочем, гонка векторизации вычислений далеко не закончена — так в последних процессорах Intel появилось новое векторное расширение AVX (Advanced Vector Extension)

Но гораздо интереснее сейчас выглядят

Графические процессоры

Теоретическая вычислительная мощность процессоров в современных видеокартах растет гораздо быстрее, чем в обычных процессорах (посмотрим знаменитую картинку от NVIDIA)

Не так давно эта мощность была приспособлена для универсальных высокопроизводительных вычислений с помощью CUDA/OpenCL.

Архитектура графических процессоров (GPGPU, General Purpose computation on GPU – универсальные расчеты средствами видеокарты), близка к уже рассмотренной SIMD.

Она называется SIMT — (single instruction, multiple threads, одна инструкция — множество потоков). Так же как в SIMD операции производятся с массивами данных, но степеней свободы гораздо больше — для каждой ячейки обрабатываемых данных работает отдельная нить команд.

В результате

1) Параллельно могут выполняться сотни операций над сотнями ячеек данных.

2) В каждом потоке выполняется произвольная последовательность команд, она может обращаться к разным ячейкам.

3) Возможны ветвления. При этом, правда, параллельно могут выполняться только нити с одной и той же последовательностью операций.

GPGPU позволяют достичь на некоторых задачах впечатляющих результатов. но существуют и принципиальные ограничения, не позволяющие этой технологии стать универсальной палочкой-выручалочкой, а именно

1) Ускорить на GPU можно только хорошо параллелящийся по данным код.

2) GPU использует собственную память. Трансфер данных между памятью GPU и памятью компьютера довольно затратен.

3) Алгоритмы с большим количеством ветвлений работают на GPU неэффективно

Мультиархитектуры-

Итак, мы дошли до полностью параллельных архитектур — независимо параллельных и по командам, и по данным.

В классификации Флинна это MIMD (Multiple Instruction stream, Multiple Data stream — Множественный поток Команд, Множественный поток Данных).

Для использования всей мощности таких систем нужны многопоточные программы, их выполнение можно «разбросать» на несколько микропроцессоров и этим достичь увеличения производительности без роста частоты. Различные технологии многопоточности давно применялись в суперкомпьютерах, сейчас они «спустились с небес» к простым пользователям и многоядерный процессор уже скорее правило, чем исключение. Но многоядерность далеко не панацея.

Суров закон, но это закон

Параллельность, это хороший способ обойти ограничение роста тактовой частоты, но у него есть собственные ограничения.

Прежде всего, это закон Амдала, который гласит

Ускорение выполнения программы за счет распараллеливания её инструкций на множестве вычислителей ограничено временем, необходимым для выполнения её последовательных инструкций.

Ускорение кода зависит от числа процессоров и параллельности кода согласно формуле

Действительно, с помощью параллельного выполнения мы можем ускорить время выполнения только параллельного кода.

В любой же программе кроме параллельного кода есть и последовательные участки и ускорить их с помощью увеличения количества процессоров не получится, над ними будет работать только один процессор.

Например, если выполнение последовательного кода занимает всего 25% от времени выполнения всей программы, то ускорить эту программу более чем в 4 раза не получится никак.

Давайте построим график зависимости ускорения нашей программы от количества параллельно работающих вычислителей-процессоров. Подставив в формулу 1/4 последовательного кода и 3/4 параллельного, получим

Грустно? Еще как.

Самый быстрый в мире суперкомпьютер с тысячами процессоров и терабайтами памяти на нашей, вроде бы даже неплохо (75%!) параллелящейся задаче, меньше чем вдвое быстрее обычного настольного четырехядерника.

Причем всё еще хуже, чем в этом идеальном случае. В реальном мире затраты обеспечение параллельности никогда не равны нулю и потому при добавлении все новых и новых процессоров производительность, начиная с некоторого момента, начнет падать.

Но как же тогда используется мощь современных очень-очень многоядерных суперкомпьютеров?

Во многих алгоритмах время исполнения параллельного кода сильно зависит от количества обрабатываемых данных, а время исполнения последовательного кода — нет. Чем больше данных требуется обработать, тем больше выигрыш от параллельности их обработки. Потому «загоняя» на суперкомп большие объемы данных получаем хорошее ускорение.

Например перемножая матрицы 3*3 на суперкомпьютере мы вряд ли заметим разницу с обычным однопроцессорным вариантом, а вот умножение матриц, размером 1000*1000 уже будет вполне оправдано на многоядерной машине.

Есть такой простой пример: 9 женщин за 1 месяц не могут родить одного ребенка. Параллельность здесь не работает. Но вот та же 81 женщина за 9 месяцев могут родить (берем максимальную эффективность!) 81 ребенка, т.е.получим максимальную теоретическую производительность от увеличения параллельности, 9 ребенков в месяц или, в среднем, тот же один ребенок в месяц на 9 женщин.

Большим компьютерам — большие задачи!

Мультипроцессор

Мультипроцессор — это компьютерная система, которая содержит несколько процессоров и одно видимое для всех процессоров. адресное пространство.

Мультипроцессоры отличаются по организации работы с памятью.

Системы с общей памятью

В таких системах множество процессоров (и процессорных кэшей) имеет доступ к одной и той же физической оперативной памяти. Такая модель часто называется симметричной мультипроцессорностью (SMP). Доступ к памяти при таком построении системы называется UMA (uniform memory access, равномерный доступ) т.к. любой процессор может обратиться к любой ячейке памяти и скорость этого обращения не зависит от адреса памяти. Однако каждый микропроцессор может использовать свой собственный кэш.

Несколько подсистем кэш-памяти процессоров, как правило, подключены к общей памяти через шину

Посмотрим на рисунок.

Что у нас хорошего?

Любой процессор обращается ко всей памяти и вся она работает одинаково. Программировать для таких систем проще, чем для любых других мультиархитектур. Плохо то, что все процессоры обращаются к памяти через шину, и с ростом числа вычислительных ядер пропускная способность этой шины быстро становится узким местом.

Добавляет головной боли и проблема обеспечения когерентности кэшей.

Когерентность кэша

Допустим, у нас есть многопроцессорный компьютер. Каждый процессор имеет свой кэш, ну, как на рисунке вверху. Пусть некоторую ячейку памяти читали несколько процессоров — и она попала к ним в кэши. Ничего страшного, пока это ячейка неизменна — из быстрых кэшей она читается и как-то используется в вычислениях.

Если же в результате работы программы один из процессоров изменит эту ячейку памяти, чтоб не было рассогласования, чтоб все остальные процессоры «видели» это обновление придется изменять содержимое кэша всех процессоров и как-то тормозить их на время этого обновления.

Хорошо если число ядер/процессоров 2, как в настольном компьютере, а если 8 или 16? И если все они обмениваются данными через одну шину?

Потери в производительности могут быть очень значительные.

Многоядерные процессоры

Как бы снизить нагрузку на шину?

Прежде всего можно перестать её использовать для обеспечения когерентности. Что для этого проще всего сделать?

Да-да, использовать общий кэш. Так устроены большинство современных многоядерных процессоров.

Посмотрим на картинку, найдем два отличия от предыдущей.

Да, кэш теперь один на всех, соответственно, проблема когерентности не стоит. А еще круги превратились в прямоугольники, это символизирует тот факт, что все ядра и кэши находятся на одном кристалле. В реальной действительности картинка несколько сложнее, кэши бывают многоуровневыми, часть общие, часть нет, для связи между ними может использоваться специальная шина, но все настоящие многоядерные процессоры не используют внешнюю шину для обеспечения когерентности кэша, а значит — снижают нагрузку на нее.

Многоядерные процессоры — один из основных способов повышения производительности современных компьютеров.

Уже выпускаются 6 ядерные процессоры, в дальшейшем ядер будет еще больше… где пределы?

Прежде всего «ядерность» процессоров ограничивается тепловыделением, чем больше транзисторов одновременно работают в одном кристалле, тем больше этот кристалл греется, тем сложнее его охлаждать.

А второе большое ограничение — опять же пропускная способность внешней шины. Много ядер требуют много данных, чтоб их перемалывать, скорости шины перестает хватать, приходится отказываться от SMP в пользу

NUMA (Non-Uniform Memory Access — «неравномерный доступ к памяти» или Non-Uniform Memory Architecture — «Архитектура с неравномерной памятью») — архитектура, в которой, при общем адресном пространстве, скорость доступа к памяти зависит от ее расположения Обычно у процессора есть » своя» память, обращение к которой быстрее и «чужая», доступ к которой медленнее.

В современных системах это выглядит примерно так

Процессоры соединены с памятью и друг с другом с помощью быстрой шины, в случае AMD это Hyper Transport, в случае последних процессоров Intel это QuickPath Interconnect

Т.к. нет общей для всех шины то, при работе со «своей» памятью, она перестает быть узким местом системы.

NUMA архитектура позволяет создавать достаточно производительные многопроцессорные системы, а учитывая многоядерность современных процессоров получим уже очень серьезную вычислительную мощность «в одном корпусе», ограниченную в основном сложностью обеспечения кэш-когерентности этой путаницы процессоров и памяти.

Но если нам нужна еще большая мощность, придется объединять несколько мультипроцессоров в

Мультикомпьютер

Мультикомпьютер — вычислительная система без общей памяти, состоящая из большого числа взаимосвязанных компьютеров (узлов), у каждого из которых имеется собственная память. При работе над общей задаче узлы мультикомпьютера взаимодействуют через отправку друг другу сообщений.

Современные мультикомпьютеры, построенные из множества типовых деталей, называют вычислительными кластерами.

Большинство современных суперкомпьютеров построены по кластерной архитектуре, они объединяют множество вычислительных узлов с помощью быстрой сети (Gigabit Ethernet или InfiniBand) и позволяют достичь максимально возможной при современном развитии науки вычислительной мощности.

Проблемы, ограничивающие их мощность, тоже немаленькие

Это:

1) Программирование системы с параллельно работающими тысячами вычислительных процессоров

2) Гигантское энергопотребление

3) Сложность, приводящая к принципиальной ненадежности

Сводим все воедино

Ну вот, вкратце пробежались почти по всем технологиям и принципам построения мощных вычислительных систем.

Теперь есть возможность представить себе строение современного суперкомпьютера.

Это мультикомпьютер-кластер, каждый узел которого — NUMA или SMP система с несколькими процессорами, каждый из процессоров с несколькими ядрами, каждое ядро с возможностью суперскалярного внутреннего параллелизма и векторными расширениями. Вдобавок ко всему этому во многих суперкомпьютерах установлены GPGPU — ускорители.

У всех этих технологий есть плюсы и ограничения, есть тонкости в применении.

А теперь попробуйте эффективно загрузить-запрограммировать всё это великолепие!

Задача нетривиальная… но очень интересная.

Что-то будет дальше?

Распределение потоков в многопоточных сетевых процессорах, основанных на однокристальных мультипроцессорах

Автор: Y.-N. Lin, Y.-D. Lin, Y.-C. Lai.

Перевод с англ.: Д.Д. Моргайлов

Источник: Lin Y.-N., Lin Y.-D., Lai Y.-C. Thread Allocation in CMP-based Multithreaded Network Processors / Y.-N. Lin, Y.-D. Lin, Y.-C. Lai // Parallel Computing. – 2010. – vol. 36 (2-3). – pp. 104-116.

1. Введение

Традиционные многопоточные-многопроцессорные архитектуры обладают тремя преимуществами: увеличение вычислительной мощности путем соединения нескольких процессорных элементов, разделение ограниченного ресурса памяти с другими элементами и формирование распределенной общей памяти, снижение накладных расходов на доступ к памяти за счет многопоточности. Однако, подсистема памяти, как правило, является узким местом системы ввиду длительных задержек доступа к ней. Современный уровень информационных технологий делает возможным расположить несколько процессоров и блоков памяти на одном чипе, что значительным образом снижает данную задержку. Такая архитектура была положена в основу многопоточных сетевых процессоров, построенных на базе однокристальных мультипроцессоров 1.

Хотя эта архитектура является перспективной, благодаря своей масштабируемости и расширяемости, в частности для некоторых сетевых процессоров 6, определение параметров архитектуры, таких как число процессоров, потоков процессора и блоков памяти, представляет собой нетривиальную задачу с учетом конкретных областей применения и показателей производительности. Кроме того, эффективная на сегодняшний день архитектура может не соответствовать требованиям ближайшего будущего в силу неравномерного развития технологий производства различных функциональных блоков. В то же время, необходимы некоторые общие рекомендации для эффективной и соответствующей целевому назначению процессора процедуры определения параметров.

Аналитические подходы широко используются во многих работах, поскольку они позволяют провести быструю оценку исследуемой системы [7]. Rafael’ем и его коллегами была предложена модель для прогнозирования производительности (с точки зрения эффективности процессора) многопоточных архитектур с различным числом потоков [8]. Эффект многопроцессорности может быть сэмулирован путем корректировки задержки при доступе к памяти, которая, предположительно, имеет геометрическое распределение. Модель обладает достаточным уровнем абстракции архитектуры, однако взаимодействие между процессорными элементами и подсистемой памяти не учитывается.

Эта проблема была устранена в [9] за счет включения в данную модель подсистемы памяти. Процессорные элементы здесь, так же, как и блоки памяти, являются распределенными и разделяемыми. Каждый поток способен выполнять полную обработку пакета и характеризуется интенсивностью обращения к локальным и отдаленным блоками памяти в процессе обработки. Тем не менее, модель не является осуществимой, так как она основана на закрытых сетях массового обслуживания. Следовательно, не рассматривается возможность приема и отправки пакетов сетевыми приложениями.

Моделирование многопоточных сетевых процессоров, построенных на основе однокристальных мультипроцессоров, рассматривается в ряде недавних работ 10. В них подробно описаны параметры архитектур и проанализированы парадигмы программирования, но не уделяется достаточного внимания обсуждению вопросов распределения потоков обработки по процессорным элементам. Lakshmanamurthy и соавторы предложили методологию для анализа производительности сетевого процессора Intel IXP2400 [4]. Однако работа посвящена исключительно оценке производительности системы: не учитывается коэффициент использования процессоров и подсистемы памяти и недостаточно исследованы подходы к проектированию сетевых процессоров.

В данной работе мы стараемся представить рекомендации для дальнейшего проектирования архитектуры путем (1) разработки аналитической модели для предварительной оценки и (2) построения среды моделирования на базе сетей Петри для проверки модели и анализа результатов проектирования. Наш подход учитывает влияние памяти и очереди готовых к выполнению на процессоре потоков, что часто игнорируется в других публикациях. Хотя установлено, что аналитическая модель не является достаточно масштабируемой для проведения глубокого изучения, результаты моделирования демонстрируют интересные зависимости в проекте. Нами предложена концепция, названная Р-М соотношением, где Р и М представляют собой вычислительные нагрузки и накладные расходы на доступ к памяти, вызванные работой приложения, и выполнена оценка зависимости между различными Р-М соотношениями и соответствующим им числом потоков на процессоре. Описаны также способы устранения эффекта «узкого места», возникающего при малых Р-М соотношениях. Parsons и Sevcik [15], Zuberek и прочие [16] рассматривают аналогичные вопросы ограничений ресурса памяти и вычислительных ограничений. Несмотря на это, статистика на уровне команд, полученная с помощью реальных образцов, не используется в качестве входных параметров моделей.

Другой особенностью нашего похода является учет схемы распределения потоков. Данные схемы определяют, как потоки процессора распределены для обработки пакетов. Выбор неподходящей схемы может привести к несбалансированной загрузке процессоров. Мы сравниваем четыре возможные схемы распределения и выбираем наиболее эффективную в качестве базового допущения нашей работы. Факторы, влияющие на выбор, включают объем аппаратных ресурсов, сложность проектирования и гибкость обработки.

2. Архитектурные допущения о схеме распределения потоков

Анализу архитектуры должно предшествовать тщательное изучение различных схем распределения потоков по процессорам. В настоящее время существует четыре схемы распределения потоков, пригодных для реализации, в которых число активных потоков процессора не превышает одного. Первая предполагает, что каждый поток отвечает за полную обработку пакета. Тем не менее, маловероятно, что нагрузка по обработке распределяется по процессорам равномерно, и поддержание порядка пакетов представляет собой сложную задачу.

На рисунке 1 приведены другие две схемы: гомогенного и гетерогенного распределения. При гомогенном распределении все потоки процессора принадлежат к одному типу, например, «приемник», «планировщик», «отправитель» и так далее. Каждый поток процессора выполняет только одну стадию обработки пакета, после чего он оповещает определенный поток следующего процессора о необходимости дальнейшей обработки. Поток процессора может иметь статическое или динамическое назначение задач. Он может работать с определенным входным портом или поддерживать при необходимости другие порты. Поскольку все потоки процессора имеют один и тот же тип, такая схема характеризуется пониженными требованиями к объему памяти для команд. Тем не менее, маловероятно, что вычислительная нагрузка будет равномерно распределена по процессорам. Также сложной задачей здесь является поддержание порядка пакетов.

Данной ситуации можно избежать, используя гетерогенное распределение потоков, при котором трафик назначается на процессоры с помощью некоторого оборудования и механизмов, балансирующих загрузку. В этой схеме потоки процессора принадлежат к разным типам и, предположительно, принимают равную нагрузку при обработке пакетов. Несмотря на то, что рассматриваемая схема требует большого объема памяти для команд, чтобы поддерживать различные задачи, в настоящее время это не является проблемой, так как большинство распространенных приложений для обработки заголовков пакетов состоят по меньшей мере из 5 тысяч команд [18], которые уже поддерживаются во многих коммерческих продуктах, как Intel IPX2400 [19] и Motorola C-5 [20]. Другим достоинством схемы являются незначительные затраты на синхронизацию, так как связь между потоками осуществляется через глобальные регистры процессора. Сравнение этих двух схем приведено в таблице 1. По описанным выше причинам сделаем предположение о гетерогенном распределении в нашей модели.

Рисунок 1 – Гомогенная (а) и гетерогенная (б) схемы распределения потоков. Число активных потоков на каждом процессоре не превышает одного

Таблица 1 – Сравнение гомогенной и гетерогенной схем